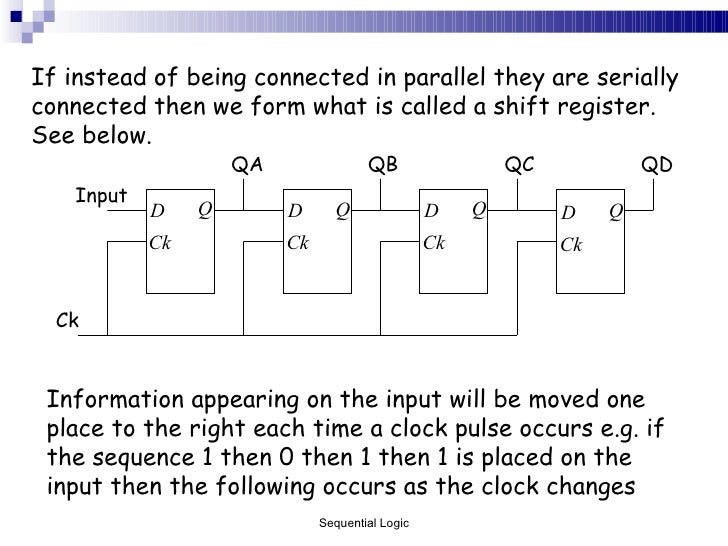

Note that each bit is shifted to the left by 1 and the new value of d is applied to LSB. In this testbench example, different values of d has to be exercised and hence a for loop is used to iterate 20 times and apply random values to the design. Then a clock is started and the stimulus is driven to the design using an initial block. The testbench follows a similar template like the one shown before where some variables are declared, design module is instantiated and connected with the testbench signals. For example, if d equals zero and the initial value of the register is 0011, it will become 0110 at the next edge of the clock clk. Shown below is a 4-bit left shift register that accepts an input d into LSB and all other bits will be shifted left by 1. Sequential circuits are those which are dependent on clock cycles and depends on present as well as past inputs to generate any output. See that the counter module counts from zero to 9, rolls over to zero and starts counting again. The stimulus simply sets default values at time 0ns, then deasserts reset after 10ns and the design is allowed to run for some time. Since the counter also requires a clock, the testbench clock is modeled with an always block. The counter module is then instantiated and connected with the testbench signals which are later driven with some values in the stimulus. The testbench first declares some variables that can be assigned some values and driven to the design inputs. Verilog parameters can be used to make a MOD-N counter which is more scalable.

Sequential logic code#

Shown below is the Verilog code for a MOD-10 counter that keeps counting up at every clock clk as long as reset rstn is deasserted. Such counters typically require log 2N number of flops to hold the count value. A MOD-N counter will count from 0 to N-1 and then roll back to zero and start counting again. Modulus(MOD) counters simply count upto a certain number before rolling back to zero. Note from the simulation wave that at the posedge of clock, output q changes value based on the state of inputs j and k as given in the truth table.

Once the loop is done, wait for some more time and finish the simulation. A for loop is used to drive different values to j and k which are driven at random times. The stimulus first initializes all inputs to the design to zero and then de-asserts reset after some time.

All other inputs to the design are of type reg so that they can be driven within a procedural block such as initial. Note that q is of type wire because it is connected to an output of the design which will be actively driving it. Then instantiate the design and connect its ports with corresponding testbench variables. The behavioral Verilog code for a JK flip-flop can be written as shown belowĪlways (posedge clk or negedge rstn) beginįirst declare all variables used in the testbench and start a clock using a simple always block that can be driven to the design. When j=1,k=1 output toggles current value When both j and k are 0, output remains the same as before When reset is asserted, output is always zero